Understanding the Deployment of Deep Learning algorithms on Embedded Platforms - Embedded Computing Design

Deep Neural Network ASICs The Ultimate Step-By-Step Guide: Gerardus Blokdyk: 9780655403975: Textbooks: Amazon Canada

Future Internet | Free Full-Text | An Updated Survey of Efficient Hardware Architectures for Accelerating Deep Convolutional Neural Networks

Arch-Net: A Family Of Neural Networks Built With Operators To Bridge The Gap Between Computer Architecture of ASIC Chips And Neural Network Model Architectures - MarkTechPost

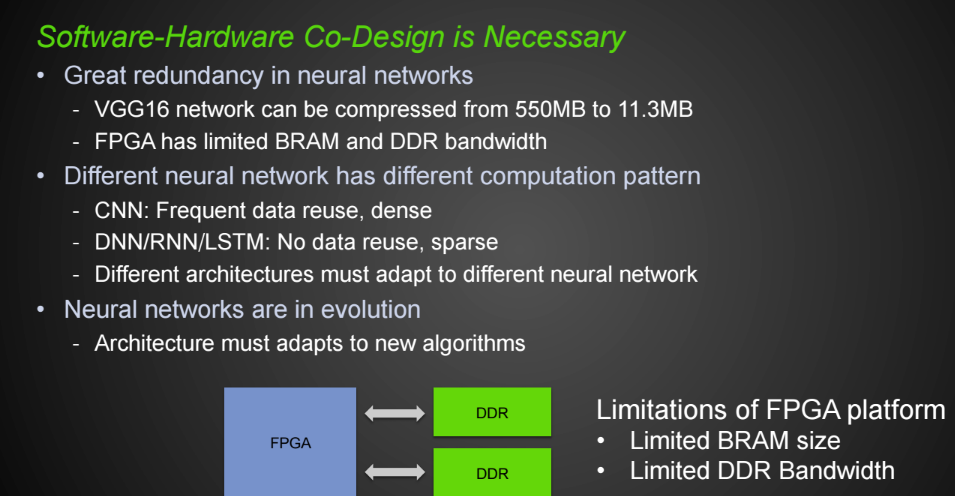

Applied Sciences | Free Full-Text | MLoF: Machine Learning Accelerators for the Low-Cost FPGA Platforms

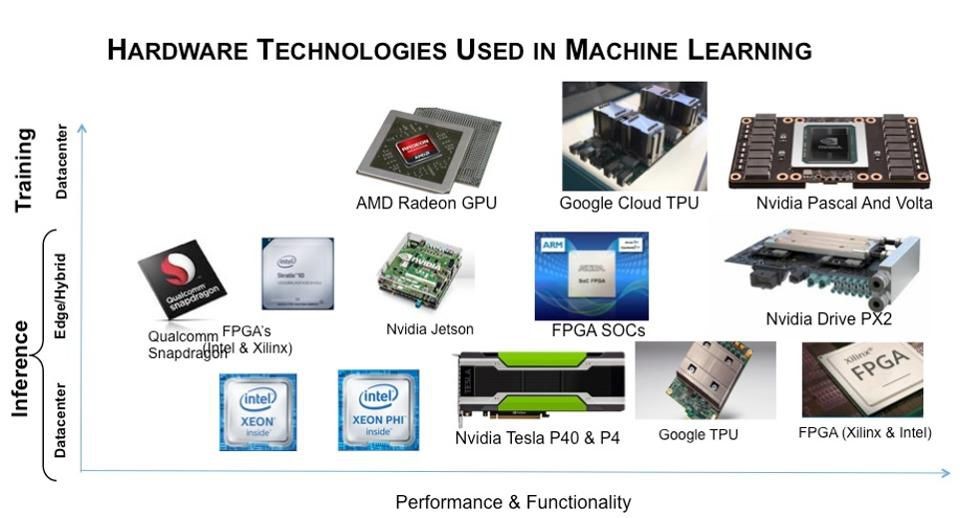

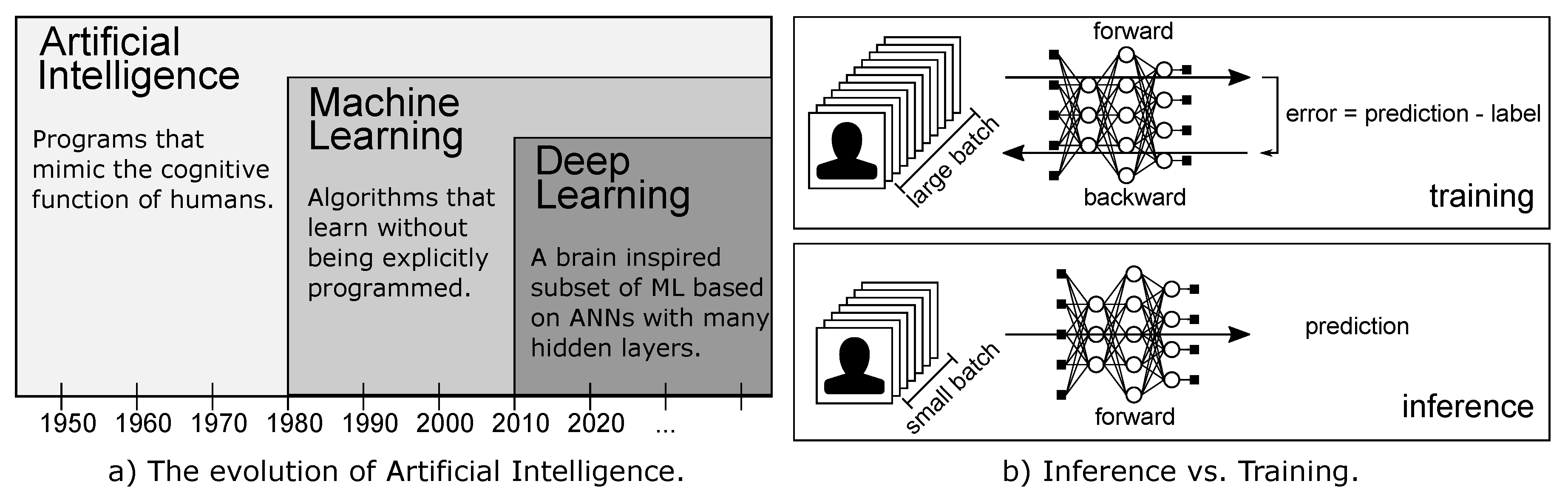

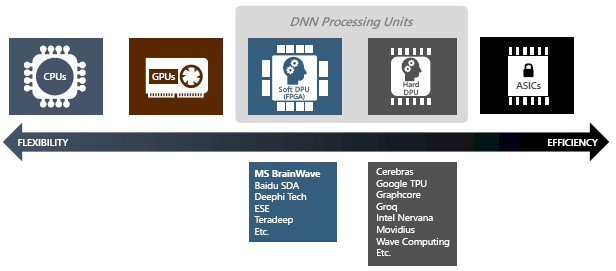

The Deep Learning Inference Acceleration Blog Series — Part 2- Hardware | by Amnon Geifman | Towards Data Science

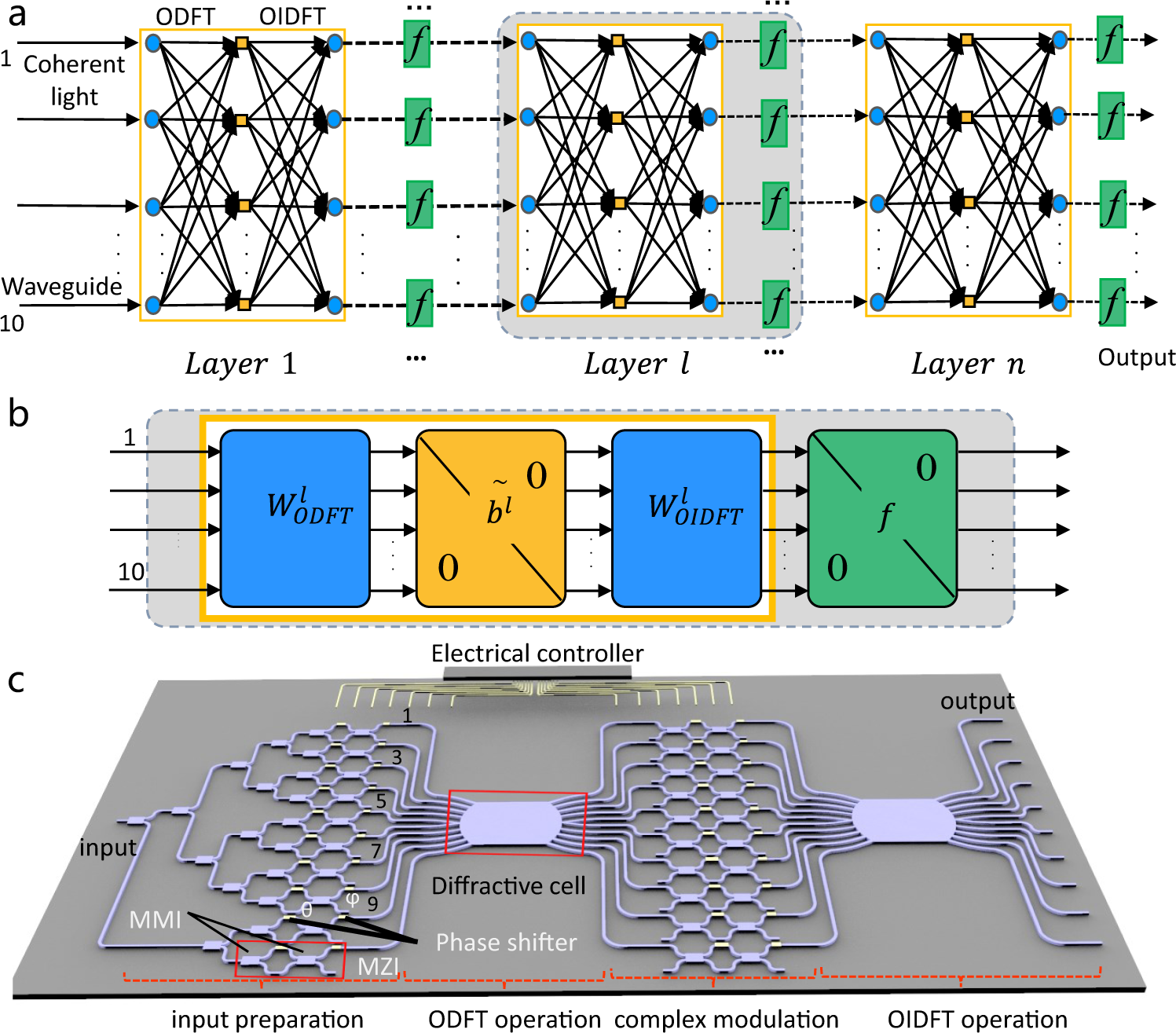

Space-efficient optical computing with an integrated chip diffractive neural network | Nature Communications

![PDF] Efficient Processing of Deep Neural Networks | Semantic Scholar PDF] Efficient Processing of Deep Neural Networks | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/64cfc87ae10e5fe178ec7c6c268c0a02eb9202ff/50-Figure2.7-1.png)